Courtesy: Xanadu

Building practical quantum computers hinges on one central challenge: error resilience. Quantum systems are inherently fragile, and even minor disturbances can corrupt computations. To overcome this, researchers rely on quantum error correction (QEC)—a foundational pillar for achieving fault-tolerant, scalable quantum computation.

Recent advances from Xanadu highlight a new framework for implementing fault-tolerant logical gates, a critical requirement for universal quantum computing. Logical gates form the smallest algorithmic units of computation, and ensuring they operate correctly even in the presence of errors is essential. The proposed approach delivers state-of-the-art performance while significantly reducing resource overhead compared to earlier methods.

Quantum Error Correction: The Foundation of Fault Tolerance

Quantum information is stored in qubits, which are highly susceptible to noise. QEC protects this information by encoding logical qubits into larger systems, known as quantum error-correcting codes, and repeatedly measuring multi-qubit operators—called stabilizers—to detect and correct errors.

Traditionally, many QEC implementations rely on topological codes, valued for their reliance on local qubit interactions. However, these codes suffer from a major drawback: as protection improves, the encoding rate—the ratio of logical qubits to physical qubits—drops toward zero, leading to substantial overhead.

Why LDPC Codes Matter

An alternative lies in low-density parity-check (LDPC) codes, which offer a more favorable scaling behavior. LDPC codes maintain a strong encoding rate even as system size increases, dramatically reducing the physical resources required for fault-tolerant quantum computing.

Xanadu’s photonic quantum architecture, which does not require strict locality between qubits, is particularly well-suited to LDPC codes. These codes are defined by stabilizers that involve only a small number of qubits, and by ensuring that no single qubit participates in too many stabilizer measurements—an important advantage, since measurements themselves introduce noise.

The Challenge of Logical Gates in LDPC Codes

While LDPC codes are attractive for error correction, they complicate the implementation of logical gates. Logical operations are typically performed by measuring logical operators that span many qubits. Directly measuring such large operators undermines fault tolerance, negating the benefits of LDPC codes.

Previous solutions introduced additional ancilla qubits to break large measurements into smaller, fault-tolerant ones. However, this often erased the resource savings gained from LDPC codes. Earlier techniques were either limited to specific codes or demanded excessive overhead.

A Homological Measurement Framework

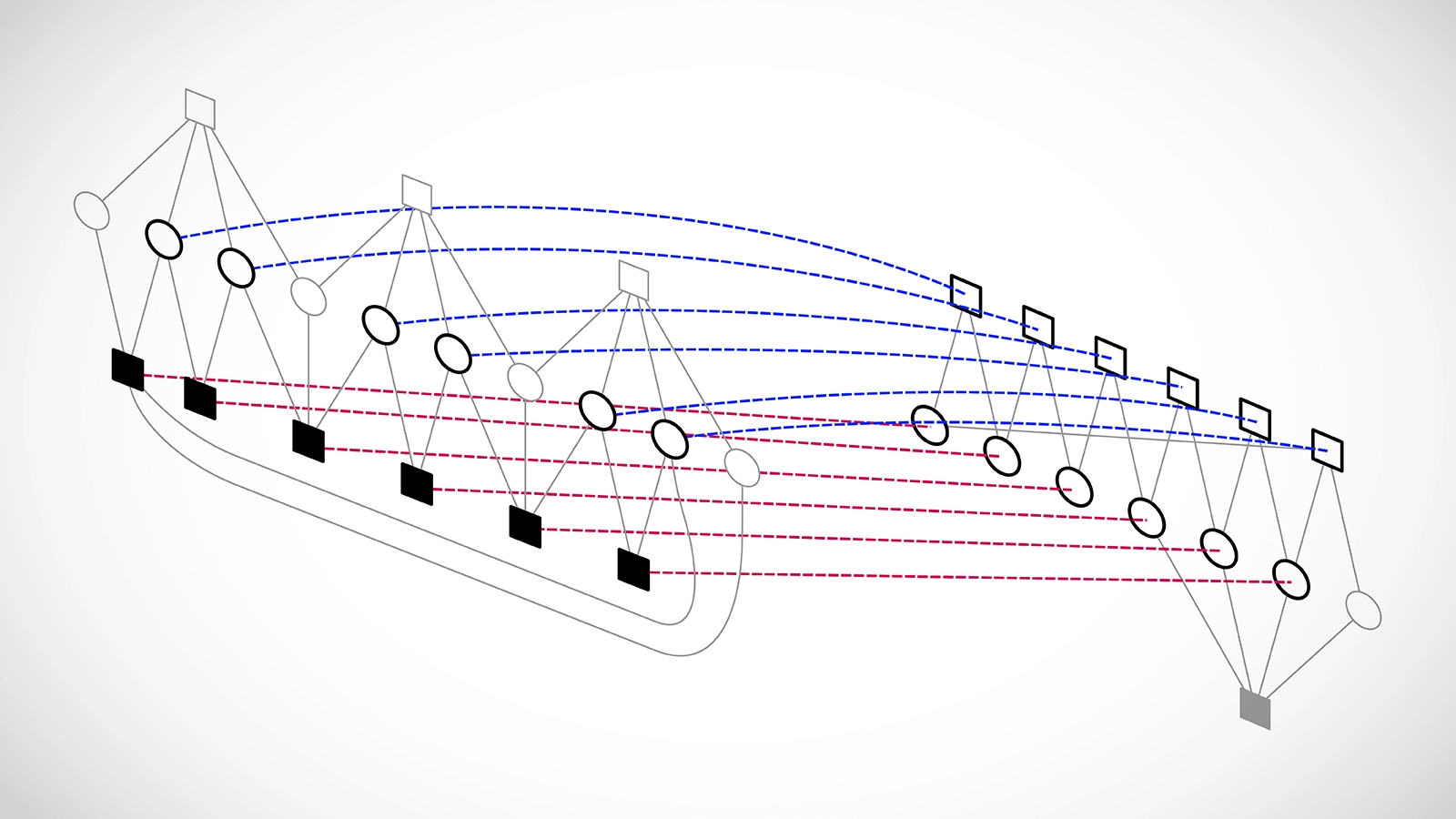

To address this, researchers developed a new homological measurement framework for quantum codes with the CSS (Calderbank–Shor–Steane) property. In these codes, stabilizers can be represented using binary matrices, which naturally map to mathematical structures known as chain complexes.

Using tools from homological algebra, this framework provides a unified way to describe both the quantum code and the ancilla systems required for logical measurements. Logical information corresponds to specific homology groups, while redundancies in stabilizer measurements are captured by other homological features.

This perspective not only encompasses most existing logical measurement techniques but also reveals clear opportunities for improvement.

Edge-Expanded Homological Measurement

Building on this framework, the work introduces an edge-expanded homological measurement technique. Each logical operator corresponds to a graph structure within the LDPC code. By selectively increasing the edge expansion—a measure of graph connectivity—the method ensures fault-tolerant measurements without significantly increasing complexity.

Crucially, this approach reduces the number of required ancilla qubits while preserving, and in some cases improving, error suppression. Simulations based on Xanadu’s photonic quantum computing architecture show that smaller systems using this method can match or outperform competing techniques that rely on substantially more resources.

Toward Scalable Fault-Tolerant Quantum Computers

By combining LDPC codes with an efficient, general-purpose framework for fault-tolerant logical gates, this work represents a meaningful step toward practical quantum computing. Reduced overhead, strong error control, and architectural compatibility suggest that large-scale fault-tolerant quantum systems may arrive sooner than previously anticipated.